Luận án Bảo mật Bitstream FPGA

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Luận án Bảo mật Bitstream FPGA", để tải tài liệu gốc về máy hãy click vào nút Download ở trên.

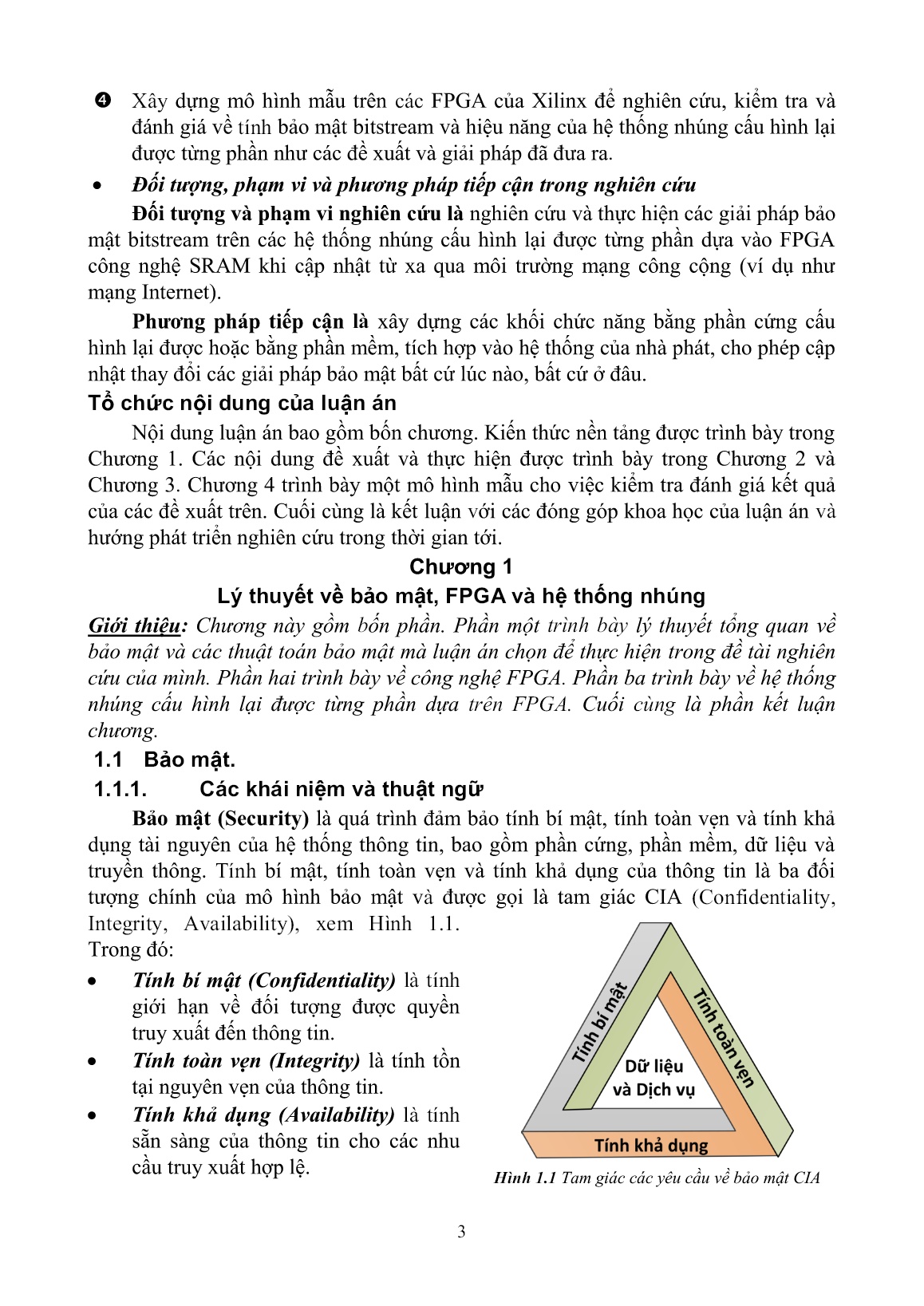

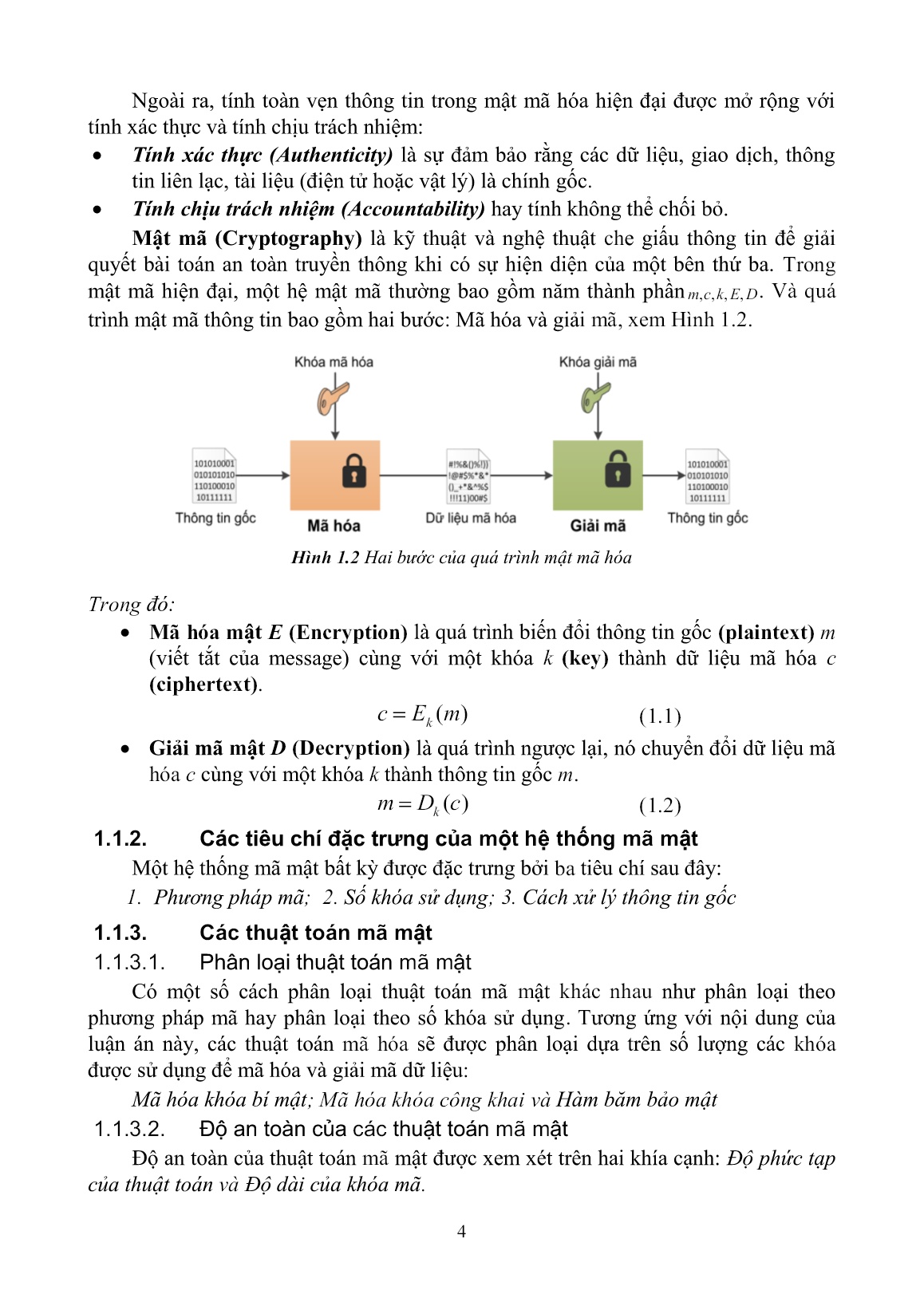

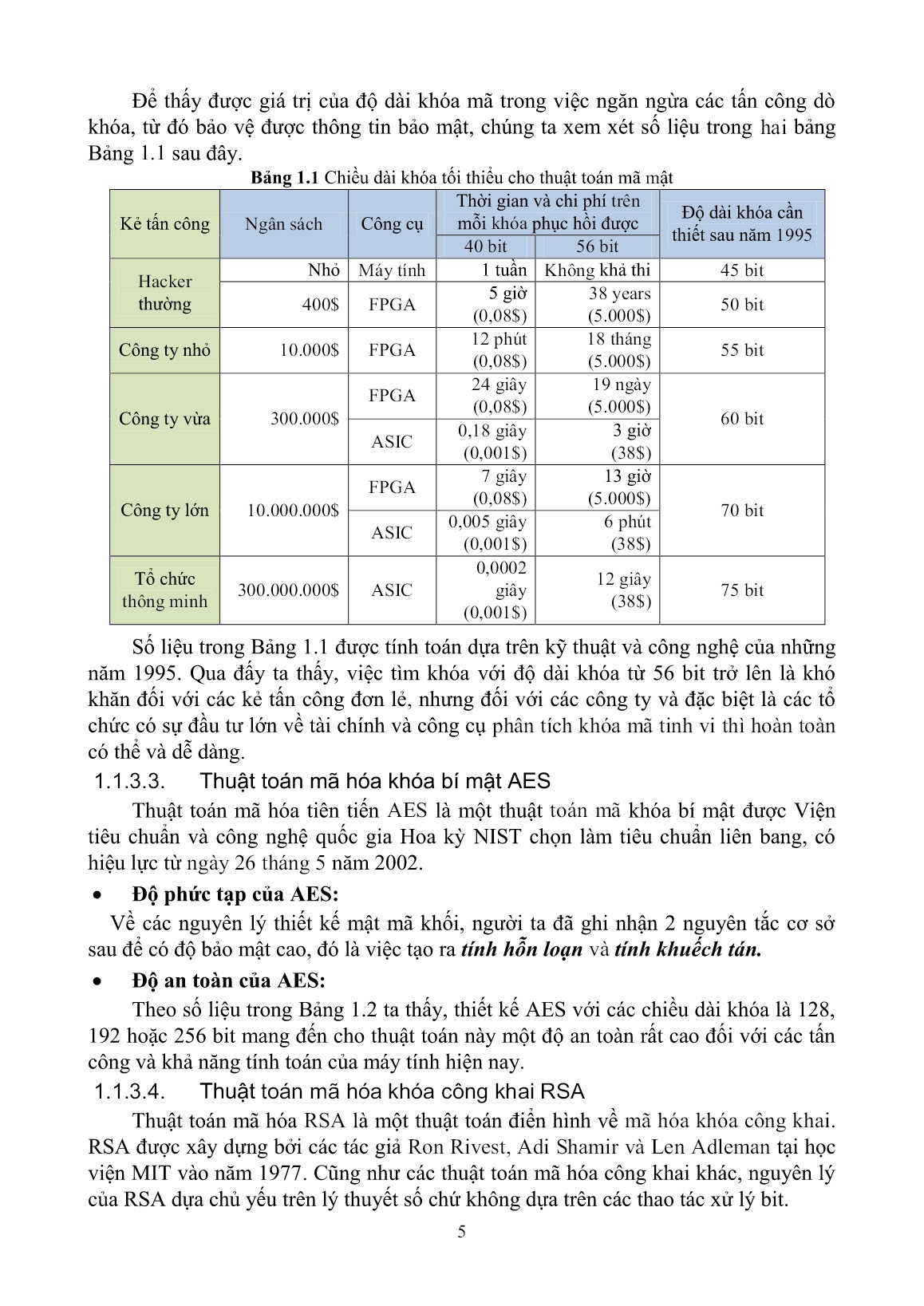

Tóm tắt nội dung tài liệu: Luận án Bảo mật Bitstream FPGA

n có kiến thức về phần cứng lẫn phần mềm. 7 1.4. Kết luận chương Thực tế cho thấy, các FPGA với các bộ vi xử lý nhúng và khả năng tái lập trình lại được sẽ cho phép xây dựng các hệ thống có hiệu suất cao. Chúng trở thành nền tảng phần cứng quan trọng, đáp ứng các mục tiêu về độ tin cậy và hiệu xuất mà một hệ thống nhúng yêu cầu. Hệ thống nhúng dựa trên SRAM-based FPGA tạo thành nền tảng công nghệ quan trọng cho thời kì hậu PC. Từ đó việc xử lý thông tin ngày càng chuyển dịch ra xa các hệ thống toàn PC và tiến về các hệ thống nhúng. Tuy nhiên, cùng với việc tăng lên của các hệ thống nhúng dựa trên FPGA, nhu cầu về bảo mật cũng tăng lên. Trong đó, bảo mật thiết kế phần cứng đặc biệt quan trọng, bởi vì nó là nền tảng mà các ứng dụng thực thi trên đó, và nó cũng là tài sản trí tuệ của các nhà thiết kế phát triển. Qua phần lý thuyết tổng quan về bảo mật, FPGA và hệ thống nhúng, chúng ta nhận thức được rằng: trong thời đại công nghiệp số hiện nay, thực hiện bảo mật là hết sức quan trọng để bảo vệ hệ thống và bảo vệ tài sản trí tuệ của người chủ sở hữu. Chương 2 Framework và giao thức cập nhật an toàn từ xa Giới thiệu: Chương này trình bày framework và giao thức mà tác giả đề xuất để đảm bảo tính an toàn và tính linh hoạt khi cập nhật bitstream từ xa của các hệ thống nhúng cấu hình lại được từng phần dựa trên FPGA. Trong framework này tác giả xem xét giải quyết các vấn đề khác nhau về bảo mật bao gồm việc trao đổi, quản lý, mã hóa, xác thực và nén bitstream. 2.1 Xây dựng và mô tả cấu trúc của Framework Để xây dựng framework và giao thức cho hệ thống nhúng cấu hình lại được từng phần, chúng ta tìm hiểu chức năng, nhiệm vụ và mối quan hệ của các chủ thể khác nhau trong quá trình trao đổi, cập nhật và bảo vệ quyền sở hữu trí tuệ các lõi IP sau đây. Nhà tích hợp hệ thống (SysInt - System Integrator): Đây là nhà thiết kế hệ thống dựa trên FPGA và cung cấp nó cho người dùng. Nhà cung cấp lõi IP (IPVend - IP Vendor): Đây là các công ty chuyên cung cấp các lõi IP có thể tái sử dụng cùng với các tài liệu liên quan. Cơ quan đáng tin cậy hay trung tâm xác thực (TAut-Trusted Authority) là cơ quan được các bên tin tưởng ủy quyền cung cấp và xác thực khóa hoặc giấy chứng nhận bản quyền. Người sử dụng hay người dùng (User): là khách hàng cuối cùng sử dụng hệ thống. Kẻ tấn công (Attacker): là đối tượng tìm cách thâm nhập, trộm cắp hoặc phá hoại các lõi IP hoặc hệ thống. Cấu trúc của framework mà luận án đề xuất được xây dựng như trong hình 2.1. 8 Hình 2.1 Cấu trúc của Framework bảo mật 2.1.1. Các thành phần phía nhà cung cấp dịch vụ - Cơ sở dữ liệu hồ sơ người sử dụng (User Profile Database) lưu trữ thông tin về tất cả người dùng đã đăng ký bao gồm cả số định danh của FPGA, phiên bản của bitstream, kích thước phân vùng cấu hình lại và thuật toán mã hóa. - Lưu trữ (Repository): Kho lưu trữ bitstream và các thành phần chức năng được sử dụng để cấu hình lại phần cứng cấu hình lại được thời gian chạy có thể được cài đặt và thực hiện trên vi xử lý nhúng của hệ thống người dùng. - Trình quản lý cập nhật của máy chủ (SuM - Server Update Manager): là trình quản lý cập nhật, thuật toán mã hóa và phần mềm. - Các bộ mã hóa, xác thực và nén: chịu trách nhiệm mã hóa, xác thực và nén bitstream. 2.1.2. Các thành phần phía người dùng Trình quản lý cập nhật của máy trạm (CuM - Client Update Manager): chịu trách nhiệm quản lý việc tải xuống và cấu hình lại hệ thống. Nó chịu trách nhiệm giao tiếp với các nhà cung cấp dịch vụ và duy trì các thông tin về hồ sơ cá nhân của hệ thống người dùng cuối. 2.2 Giao thức cập nhập Giao thức cập nhật xác định một cuộc tương tác trao đổi giữa một trình quản lý cập nhật máy chủ SuM của bên cung cấp dịch vụ, là thực thể phụ trách việc phân phối bitstreams mới tới các hệ thống nhúng dựa trên FPGA, và một trình Hình 2.2 Lưu đồ giao thức cập nhật an toàn 9 quản lý cập nhật máy khách CuM của phía người sử dụng. Hình 2.2 mô tả thông tin liên lạc giữa SuM và CuM. Mỗi phiên giao dịch bắt đầu với một bản tin "GetUpdate" ban đầu từ SuM và một bản tin phản hồi "ResUpdate" từ CuM. Trong các bản tin "GetUpdate" và "ResUpdate", hai bên trao đổi các tham số cần thiết cho một phiên cập nhật an toàn, ví dụ như số chỉ dùng một lần "Nonces", số định danh FPGA F, phiên bản bitstream V, số giấy phép bản quyền NPiLS, v.v. Sau đó, các tham số này được chuyển đổi một cách gián tiếp vào trong các mã xác thực bản tin MAC thông qua việc thực hiện hàm băm SHA. Điều này đảm bảo rằng việc xác thực sự tươi mới của dữ liệu nhận được tiếp theo trong phiên giao dịch chỉ đơn giản là dùng mỗi giá trị MAC mà không cần phải lặp lại các tham số và dữ liệu cũ của đã trao đổi trước đó. 2.2.1. Giao thức cập nhật từ xa an toàn Giao thức cập nhật từ xa an toàn bao gồm hai thuật toán tương ứng với hai phía của một hệ thống: Thuật toán 1 cho phía FPGA (tức là phía người sử dụng) và thuật toán 2 cho phía nhà cung cấp dịch vụ. Đầu tiên, chúng ta tập trung thảo luận về các thuật toán 1 ở phía FPGA, đây là thuật toán chạy trên thiết bị với nhiều hạn chế về tài nguyên phần cứng. Các tham số trong giao thức được lưu trữ trong cơ sở dữ liệu hồ sơ người dùng của nhà cung cấp dịch vụ và bên phía người sử dụng. Các tham số đó là: SKS: Khóa bảo mật được chia sẻ bởi SuM F: Số định danh của FPGA Pi: Số định danh của phân vùng cấu hình lại được trong FPGA VPi: Số phiên bản của bitstream hiện đang hoạt động Lmax: Độ dài tối đa của bitstream từng phần của phân vùng Pi AE: Thuật toán mã hóa được sử dụng AC: Thuật toán nén được sử dụng VPiNVM: Số phiên bản bitsream lưu trữ trong bộ nhớ không bay hơi NCuM: Giá trị bộ đếm lưu trong bộ nhớ không bay hơi của CuM LPiU: Độ dài bitstream từng phần được tải lên NPiLS: Số bản quyền của bitstream từng phần VPiU: Số phiên bản của bitstream được tải lên NSuM: Số Nonce được tạo bởi SuM Fe, Pe, Ve: Giá trị được mong đợi của F, Pi,VPi Nmax: Giới hạn trên của NNVM PB: Bitstream từng phần ở dạng nén Mx: Các giá trị MACs 2.2.2.1. Thuật toán 1 - Thuật toán bên phía người dùng FPGA 1. Start: 2. Receive(C, Fe, Pi, VPie, LPiU, Nmax, NSuM, M0) 3. if LPiU Lmax then goto 34 4. if C ≠ “GetUpdate” then goto Start: 5. VPiNVM := VPi 6. ReadNVM(NCuM) 10 7. M’0 = MAC(C, Fe, Pi, VPie, LPiU, Nmax, NSuM) 8. S := (M0 = M’0) (VPie = VPi) (Fe = F) (NCuM < Nmax) 9. if S then 10. NCuM := NCuM + 1 11. WriteNVM(NCuM) 12. else goto Start: 13. end if 14. MK := MAC(F, Pi, VPi, SKS) 15. MLS := MAC(F, Pi, VPi, NPiLS) 16. M1 := MAC(“ResUpdate”, F, Pi, VPi, Lmax, NCuM, AE, AC, MK, MLS, M0) 17. Send(“ResUpdate”, F, Pi, VPi, Lmax, NCuM, AE, AC, MK, MLS, M1) 18. Receive(C, M2) 19. if M2 ≠ MAC(C, M1) then goto Start: 20. if C = “Update” then 21. Receive(PB, M3) 22. If M3 ≠ MAC(PB, M2) then goto Start: 23. Receive(“UpFinish”, VPiU, M4) 24. if M4 ≠ MAC(“UpFinish”, VPiU, M3) then goto Start: 25. Decrypt() 26. Decompress() 27. ReconfCtr() 28. VPiNVM := VPi 29. M5 = MAC(“UpConfirm”, VPiNVM, M4) 30. Send(“UpConfirm”, VPiNVM, M5) 31. end if 32. if C= “Abort” then goto Start: 33. UpUserprofile(F, Pi, VPi, Lmax, NCuM, AE, AC) 34. Warn(“Resize your partial reconfigurable partition”) Trong đó: - GetUpdate, Update, UpFinish, Abort là các bản tin được gửi từ máy chủ cập nhật. - ResUpdate, UpConfirm là các bản tin được gửi từ FPGA đến máy chủ cập nhật. - Decrypt(), Decompress(), ReconfCtr() là các hàm giải mã, giải nén và cấu hình lại. - UpUserprofile là chỉ thị lệnh cập nhật hồ sơ người dùng. 2.2.2. Phân tích bảo mật 2.2.3.1. Tính bí mật và tính xác thực Trong giao thức đã đề xuất, ở phía FPGA, bộ giải mã và bộ xác thực luôn luôn được thực hiện và có thể thực hiện trong phần cứng hoặc phần mềm nhúng. Do vậy, bitstream một phần được chuyển giao thông qua Internet luôn được mã hóa để chống lại các cuộc tấn công nhân bản hoặc kỹ thuật đảo ngược. Các bước trong quá trình trao đổi này luôn được xác thực để đảm bảo tính tươi mới, tính toàn vẹn và tính chính gốc của bitstream, nhằm ngăn chặn các cuộc tấn công phát lại. 2.2.3.2. Giá trị của các tham số NSuM là số ngẫu nhiên đủ lớn để việc tái hiện lại nó thông thực tế là không thể. Việc sử dụng một từ 64-bit cho NSuM sẽ đảm bảo rằng một kẻ tấn công với năng lực thực hiện 103 truy vấn mỗi giây phải mất vài thập kỷ để tìm ra một giá trị trùng lặp. 11 Giao thức đề xuất sử dụng khóa SKS dài 256-bit cho thuật toán mã hóa AES. Thuật toán AES cho đến nay vẫn được coi là an toàn, có nghĩa là trong hiện tại dữ liệu được mã hóa với thuật toán AES đã không bị phá vỡ. Chiều dài khóa 256-bit của thuật toán AES là đủ để bảo vệ thông tin thuộc loại bí mật. Các giá trị MAC M0, M1, M2, M3,v.v. được tạo ra bởi hàm băm SHA-512 có chiều dài 512-bit. Các giá trị MAC này cung cấp một mức an toàn cao đối với các cuộc tấn công dò tuần tự. Các tham số khác như Pi, Vi, LMax, v.v. là các tham số phục vụ cho việc cấu hình lại từng phần. Kích thước của chúng phụ thuộc vào các ứng dụng và định nghĩa của người dùng. 2.3 Giao thức trao đổi khóa 2.3.1. Giao thức trao đổi khóa qua trung tâm xác thực Đây là mức độ an toàn rất cao trong trao đổi khóa. Khóa của các bên luôn luôn được chứng thực bởi trung tâm xác thực trước khi thực hiện giao dịch dữ liệu. Chi tiết được mô tả trong Hình 2.3 và các bước tiến hành như sau: Hình 2.2 Giao thức trao đổi khóa được xác thực bởi TAut Tại mỗi phiên giao dịch, cả hai khóa PKV và SKS luôn được trao đổi và xác thực qua TAut. Riêng khóa riêng SKV là không trao đổi. Khóa công khai PKV không cần phải giữ bí mật nên khi trao đổi qua mạng không cần thiết phải được mã hóa. Chỉ khóa bí mật SKS cần phải được bảo mật và nó đã được mã hóa bởi khóa PKV trước khi gửi qua Internet. Giao thức trao đổi khóa an toàn được mô tả chi tiết hơn trong các thuật toán sau. 2.3.1.1. Thuật toán 3 - Thuật toán bên phía nhà thiết kế hệ thống S1. Generate(NSuM) S2. M0 = HMAC(“ReqIP”, SID, VID, NSuM) S3. Send(“ReqIP”, SID, VID, NSuM, M0) S4. Receive(“ReqSKS”, PKV, M1) S5. M1’ = HMAC(“ReqSKS”, PKV, M0) S6. If M1’ ≠ M1 then goto S1 S7. M2 = HMAC(“VerifyPKV”, SID, VID, TAID, PKV, M1) S8. Send(“VerifyPKV”, SID, VID, TAID, PKV, M1, M2) S9. Receive(“ConfirmPKV”, M3) S10. M3’ = HMAC(“ConfirmPKV”, M2) S11. If (“ConfirmPKV ” ≠ PKV_OK) or M3’ ≠ M3 then goto S1 12 S12. M4 = HMAC(EncryptedSKS, M1) S13. Send(EncryptedSKS, M4) S14. Receive(EncryptedIP, M7) 2.3.1.2. Thuật toán 4 – Thuật toán bên phía nhà cung cấp IP V1. Receive(“ReqIP”, SID, VID, NSuM, M0) V2. M0’ = HMAC(“ReqIP”, SID, VID, NSuM) V3. If M0’ ≠ M0 then goto V1 V4. M1 = HMAC(“ReqSKS”, PKV, M0) V5. Send(“ReqSKS”, PKV, M1) V6. Receive(EncryptedSKS, M4) V7. M4’ = HMAC(EncryptedSKS, M1) V8. If M4’ ≠ M4 then goto V1 V9. M5 = HMAC(“VerifySKS”, EncryptedSKS, M4) V10. Send(“VerifySKS”, EncryptedSKS, SID, VID, PKV, M4, M5) V11. Receive(“ConfirmSKS”, M6) V12. M6’ = HMAC(“ConfirmSKS”, M5) V13. If (“ConfirmSKS ” ≠ SKS_OK) or M6’ ≠ M6 then goto V1 V14. M7 = HMAC(EncryptedIP, M6) V15. Send(EncryptedIP, M7) 2.3.1.3. Thuật toán 5 – Thuật toán bên phía trung tâm xác thực T1. Receive(“VerifyPKV”, SID, VID, TAID, PKV, M1, M2) T2. M2’ = HMAC(“VerifyPKV”, SID, VID, TAID, PKV, M1) T3. If M2’ ≠ M2 then goto T1 T4. M3 = HMAC(“ConfirmPKV”, M2) T5. Send(“ConfirmPKV”, M3) T6. Receive(“VerifySKS”, EncryptSKS, SID, VID, PKV, M4, M5) T7. M5’ = HMAC(“VerifySKS”, EncryptedSKS, M4) T8. If M5’ ≠ M5 then goto T1 T9. M6 = HMAC(“ConfirmSKS”, M5) T10. Send(“ConfirmSKS”, M6) 2.3.2. Giao thức trao đổi khóa qua không qua trung tâm xác thực Hình 2.3 Giao thức trao đổi khóa không qua trung tâm xác thực 13 Khi các bên có thể tin tưởng lẫn nhau, trao đổi khóa có thể không cần phải qua trung tâm xác thực. Tuy nhiên, để phòng ngừa rủi ro, khóa đối xứng theo phiên (sau đây gọi là khóa phiên) được đề xuất sử dụng. Khóa phiên là một khóa đối xứng có thể được sử dụng cho từng trao đổi khác nhau giữa các đối tác. Khóa được tạo ra cho mỗi phiên giao dịch để loại bỏ các yêu cầu về bảo trì và lưu trữ. Mỗi một khoá được sử dụng một lần với một bản tin duy nhất. Các thuật toán của việc trao đổi khóa an toàn giữa SysInt và IPVend, Hình 2.4a, hoặc giữa SysInt và User, Hình 2.4b, được mô tả như dưới đây. trong đó, khóa phiên SSKS được tạo ra bởi SysInt. SysInt sử dụng PKV để mã hóa khóa phiên này và gửi cho IPVend. 2.3.2.1. Thuật toán 6: Thuật toán bên phía nhà tích hợp hệ thống S1. Generate(NSuM, SSKS) S2. M0 = HMAC(“ReqIP”, SID, VID, NSuM) S3. Send(“ReqIP”, SID, VID, NSuM, M0) S4. Receive(“ReqSSKS”, PKV, M1) S5. M1’ = HMAC(“ReqSSKS”, PKV, M0) S6. If M1’ ≠ M1 then goto S1 S7. M2 = HMAC(EncryptedSSKS, M1) S8. Send(EncryptedSSKS, M2) S9. Receive(EncryptedIP, M3) 2.3.2.2. Thuật toán 7: Thuật toán bên phía nhà cung cấp IP V1. Receive(“ReqIP”, SID, VID, NSuM, M0) V2. M0’ = HMAC(“ReqIP”, SID, VID, NSuM) V3. If M0’ ≠ M0 then goto V1 V4. M1 = HMAC(“ReqSSKS”, PKV, M0) V5. Send(“ReqSSKS”, PKV, M1) V6. Receive(EncryptedSSKS, M2) V7. M2’ = HMAC(EncryptedSSKS, M1) V8. If M2’ ≠ M2 then goto V1 V9. M3 = HMAC(EncryptedIP, M2) V10. Send(EncryptedIP, M3) 2.3.3. Phân tích bảo mật Độ an toàn và tính bảo mật của các tham số NSuM, độ dài khóa và các thuật toán mã hóa tương tự như đã phân tích ở phần trên 2.2.3. Phân này phân tích tiếp một số bổ sung trong giao thức trao đổi khóa an toàn. Khóa của các thiết bị cụ thể có thể được tạo ra và quản lý theo nhiều cách khác nhau. Ví dụ, SKS có thể được tạo ra và xác thực bởi TAut, và được lưu trữ trong cơ sở dữ liệu của máy chủ cập nhật. Hoặc khóa phiên SSKS có thể được tính toán từ số định danh F và số chỉ sử dụng một lần NSuM: 14 SSK E(,) F N (2.1) S KM SuM Trong đó khóa KM chỉ được biết đến bởi máy chủ cập nhật. Hoặc theo một cách khác, số định danh F có thể được sử dụng như một khóa công khai để các máy chủ cập nhật trao đổi an toàn khóa bí mật SKS, SSKS với các thiết bị đầu cuối. Thuật bất đối xứng RSA được sử dụng để bảo vệ khóa đối xứng khi trao đổi qua mạng. Việc tìm khóa riêng từ khóa công khai đã biết là rất khó khăn. Hơn nữa, khóa riêng không được trao đổi qua mạng, do đó nguy cơ bị rò rỉ khóa này là ít có thể xảy. Có nghĩa là việc bảo vệ khóa đối xứng khi trao đổi qua mạng bằng thuật toán khóa công khai sẽ là cách thực hiện rất an toàn. 2.4 Đánh giá và so sánh với các nghiên cứu liên quan Các nghiên cứu trước đây vẫn chưa xem xét một cách đầy đủ các khía cạnh của một giải pháp tổng thể cho bài toán bảo mật bitstream trong các hệ thống nhúng cấu hình lại được từng phần dựa trên FPGA khi cập nhật từ xa qua mạng công cộng với nhiều rủi ro trên đường truyền dẫn. Đó là lý do mà tác giả đã đề xuất framework và xây dựng giao thức cập nhật an toàn như đã trình bày ở trên. Kết quả cụ thể được chỉ ra trong Bảng 2.1 sau. Bảng 2.1 So sánh các thực hiện trên bitstream và hệ thống Giao thức Trao Cấu hình Mã Xác Hệ thống Các nghiên cứu Nén cập nhật đổi từng hóa thực nhúng từ xa khóa phần [23] x x x [30] x x x [41] x x x [90][91] x [93][94] x x [95] x x Framework của x x x x x x x chúng tôi 2.5 Kết luận chương Qua chương này, tác giả đã thực hiện hai công việc chính. Đó là: - Đã đề xuất và trình bày một framework cho việc bảo mật bitstream của các hệ thống nhúng cấu hình lại được từng phần dựa trên FPGA khi cập nhật từ xa qua mạng internet. Framework của tác giả là cấu trúc hoàn chỉnh và linh hoạt dành cho các nhà thiết kế hệ thống cũng như người dùng khi thực hiện các giải pháp an ninh cho hệ thống của mình. - Một phần quan trọng trong framework là giao thức truyền thông an toàn và các cơ chế đảm bảo an toàn cập nhật bitstream. Tác giả đã đề xuất và xây dựng một bộ giao thức với các tình huống trao đổi và cập nhật bitstream khác nhau. Giao 15 thức này với các tham số đáp ứng cho việc cập nhật an toàn hệ thống nhúng cấu hình lại được từng phần mà một số nghiên cứu trước đây chưa đề cập đến. Chương 3 Nâng cao hiệu năng và tính linh hoạt trong bảo mật bitstream của hệ thống cấu hình lại được từng phần dựa trên FPGA Giới thiệu: Chương này tác giả xem xét đến việc sử dụng tối ưu tài nguyên của hệ thống bằng cách đề xuất giải pháp xây dựng các bộ giải mã và xác thực trong khu vực cấu hình lại được từng phần. Các mã hóa này có thể được giải phóng khỏi khu vực cấu hình lại khi nó không được sử dụng đến và thay thế vào đó bằng một ứng dụng hữu ích khác. Ngoài ra, để giảm dung lượng bộ nhớ khi lưu trữ bitstream, tác giả sử dụng giải pháp nén bitstream. Và để cải thiện hiệu năng của hệ thống, tác giả sử dụng bus tốc độ cao AXI với các bộ FIFO được hỗ trợ trong các FPGA hiện đại. 3.1 Hệ thống cấu hình lại được từng phần Cấu hình lại được từng phần là khả năng thay đổi một cách linh hoạt các khối logic phần cứng bằng cách cấu hình lại các phân vùng tương ứng trên thiết bị bằng các tập tin bitstream từng phần. Với công nghệ cấu hình lại được từng phần, phần cứng của FPGA được thiết kế gần giống như thiết kế phần mềm. Có nghĩa là, nó có thể được thiết kế thành từng mô- đun cấu hình lại được RM (Reconfigurable Module), và sau đó tổng hợp vào hệ thống. Như được trình bày trong Hình 3.1, hệ thống cấu hình lại được từng phần dựa trên FPGA bao gồm phần logic tĩnh và ba phân vùng cấu hình lại được RP (Reconfigurable Hình 3.1 Ví dụ về một hệ thống cấu hình Partition). Ứng với các phân vùng RP#1, lại được từng phần RP#2, RP#3, ta có thể xây dựng thành tập các mô-đun từng phần RM1, RM1,RM3 tương ứng. 3.1.1. Các ưu điểm của cấu hình lại từng phần Có rất nhiều lợi ích với cấu hình lại từng phần: - Tăng hiệu năng của hệ thống - Khả năng thay đổi phần cứng - Chia sẻ phần cứng - Giảm thời gian cấu hình lại 3.2 Tối ưu hóa tài nguyên phần cứng 3.2.1. Tối ưu hóa tài nguyên logic 16 Trong thiết kế bảo mật, tác giả xây dựng các bộ mã hóa, xác thực và nén bitstream trong phần cứng và cả trong phần mềm. Đối với phần cứng, tác giả xây dựng các bộ mã hóa và xác thực trong phần logic cấu hình lại được. Sơ đồ của hệ thống như được thể hiện trong Hình 3.2. 3.2.1.1. Phân tích và đánh giá kết quả Sự linh động và tiết kiệm tài nguyên cho hệ thống có thể được giải thích như sau: - Các bộ mã hóa AES và xác thực SHA có thể được phát triển, nâng Hình 3.2 Sơ đồ khối của hệ thống nhúng cấu cấp và tái sử dụng một cách linh hình lại được dựa trên FPGA động mỗi khi có yêu cầu mà không cần phải thiết kế lại toàn bộ hệ thống. - Như số liệu trong Bảng 3.1, ta thấy tài nguyên sử dụng cho AES-256 và SHA- 512 chiếm một phần đáng kể trong FPGA Spartan-6 của Xilinx. Việc giải phóng các phần tài nguyên này thực sự cần thiết và hữu ích. Bảng 3.1 Sử dụng phần cứng của AES-256 và SHA-512 Tài nguyên sử dụng Lõi IP Registers LUTs Slice AES-256 3.096 (5,67%) 3.751 (13,74%) 1.293 (18,95%) SHA-512 2.246 (4,11%) 2.299 (8,42%) 848 (12,48%) 3.2.2. Tối ưu vùng nhớ lưu trữ Nén bitstream là một công việc quan trọng trong thiết kế hệ thống cấu hình lại vì nó làm giảm kích thước bitstream để giảm yêu cầu về bộ nhớ lưu trữ. Nó cũng cải thiện băng thông truyền tải trên mạng và do đó giảm được thời gian cập nhật hệ thống. Đặc biệt là trong các hệ thống cấu hình lại được từng phần. Tỉ số nén thường được sử dụng để tính toán hiệu quả của các kỹ thuật nén và được định nghĩa như sau: CP CR (3.1) OP Trong đó CR (Compression Ratio) là tỉ số nén, CP (Compressed Program) kích thước chương trình đã nén, OP (Original Program) kích thước chương trình gốc ban đầu. Như vậy, thuật toán nén tốt sẽ có tỉ số

File đính kèm:

luan_an_bao_mat_bitstream_fpga.pdf

luan_an_bao_mat_bitstream_fpga.pdf