Luận án Nghiên cứu xây dựng bộ điều khiển CNC–ON–CHIP

Trang 1

Trang 2

Trang 3

Trang 4

Trang 5

Trang 6

Trang 7

Trang 8

Trang 9

Trang 10

Tải về để xem bản đầy đủ

Bạn đang xem 10 trang mẫu của tài liệu "Luận án Nghiên cứu xây dựng bộ điều khiển CNC–ON–CHIP", để tải tài liệu gốc về máy hãy click vào nút Download ở trên.

Tóm tắt nội dung tài liệu: Luận án Nghiên cứu xây dựng bộ điều khiển CNC–ON–CHIP

c và chức năng bộ điều khiển CNC

Về cơ bản, bộ điều khiển CNC được mô tả cấu tạo, hình dáng

gồm có 3 thành phần: Phần giao diện người – máy (MMI), phần lõi

điều khiển (NCK) và phần điều khiển logic khả trình (PLC).

1.1.4 Công cụ lập trình bộ điều khiển CNC1

Hai công cụ trình bày là công cụ băng tay (G-code) và công cụ tự

động (APT).

1.2 Một số nghiên cứu liên quan đến luận án

1.2.1 Tình hình nghiên cứu trên thế giới

Những nghiên cứu phát triển thuật toán: Các nghiên cứu này đi

vào đơn lẻ, các ếk t quả mô phỏng, khó có thể thực hiện trên bộ điều

khiển công nghiệp. Bởi nó đòi hỏi can thiệp sâu vào nhà chế tạo, sử

dụng các thuật toán phần mềm, khó khăn cho việc cài đặt vào hệ

thống điều khiển trước đây. Vì vậy, hướng nghiên cứu thay đổi công

nghệ phần cứng là một nhiệm vụ trọng tâm luận án này.

1 Nội dung các tiểu mục được trình bày chi tiết hơn trong cuốn toàn văn luận án.

4

Nghiên cứu ứng dụng công nghệ: Đánh giá những nghiên cứu

công nghệ cho thấy, cần thiết đưa công nghệ FPGA vào việc thiết kế,

xây dựng bộ điều khiển CNC. Sử dụng FPGA cho tốc độ cao, đáp

ứng yêu cầu thời gian thực của bộ điều khiển CNC. Hạn chế khi sử

dụng FPGA là thiết kế đầy đủ các chức năng bộ điều khiển CNC cần

rất nhiều tài nguyên phần cứng và xử lý các phép toán số thực chưa

hiệu quả bằng phần mềm. Vì vậy, kết hợp FPGA với lõi mềm là

hướng đi phù hợp trong việc chế tạo bộ điều khiển CNC.

Nghiên cứu tích hợp công nghệ: Xu hướng các bộ điều khiển ngày

được chế tạo tích hợp từ card gắn trên PC, tiến đến các “on board”

nhằm giảm kích thước, giá thành, nâng cao độ tin cậy và tốc độ

truyền thông của bộ điều khiển CNC. Vì vậy, tác giả xây dựng bộ

điều khiển CNC-on-Chip là hướng đi phù hợp.

1.2.2 Tình hình nghiên cứu trong nước

Kết luận những nghiên cứu trong nước: Nhìn chung, các thiết bị

CNC đã được nghiên cứu nhiều ở Việt Nam, cụ thể:

- Nhóm nghiên cứu thứ nhất về cơ khí: Đây là nhóm nghiên cứu

chiếm đa số các công trình có liên quan đến gia công CNC. Những

nghiên cứu này phần lớn đi vào thực nghiệm, một số ít xây dựng dựa

trên điều khiển máy tính; ấv n đề thời gian thực và thuật toán chưa

được xem xét trên thiết bị điều khiển CNC.

- Nhóm nghiên cứu thứ hai về thiết bị điều khiển cho máy công

cụ, các thiết bị điều khiển được tập trung nghiên cứu hơn so với

nhóm thứ nhất. Tuy nhiên, các nghiên cứu chỉ thực hiện các thành

phần đơn lẻ của bộ điều khiển CNC. Các vấn đề về ứng dụng công

nghệ mới, khả năng tích hợp các thành phần hay các nghiên cứu về

thuật toán ềđi u khiển chưa được đề cập. Vì vậy, tác giả lựa chọn

nghiên cứu theo nhóm thứ hai cho luận án này.

5

1.3 Lựa chọn đối tượng CSoC cho bộ điều khiển CNC-on-Chip

1.3.1 Đề xuất cấu trúc bộ điều khiển CNC-on-Chip

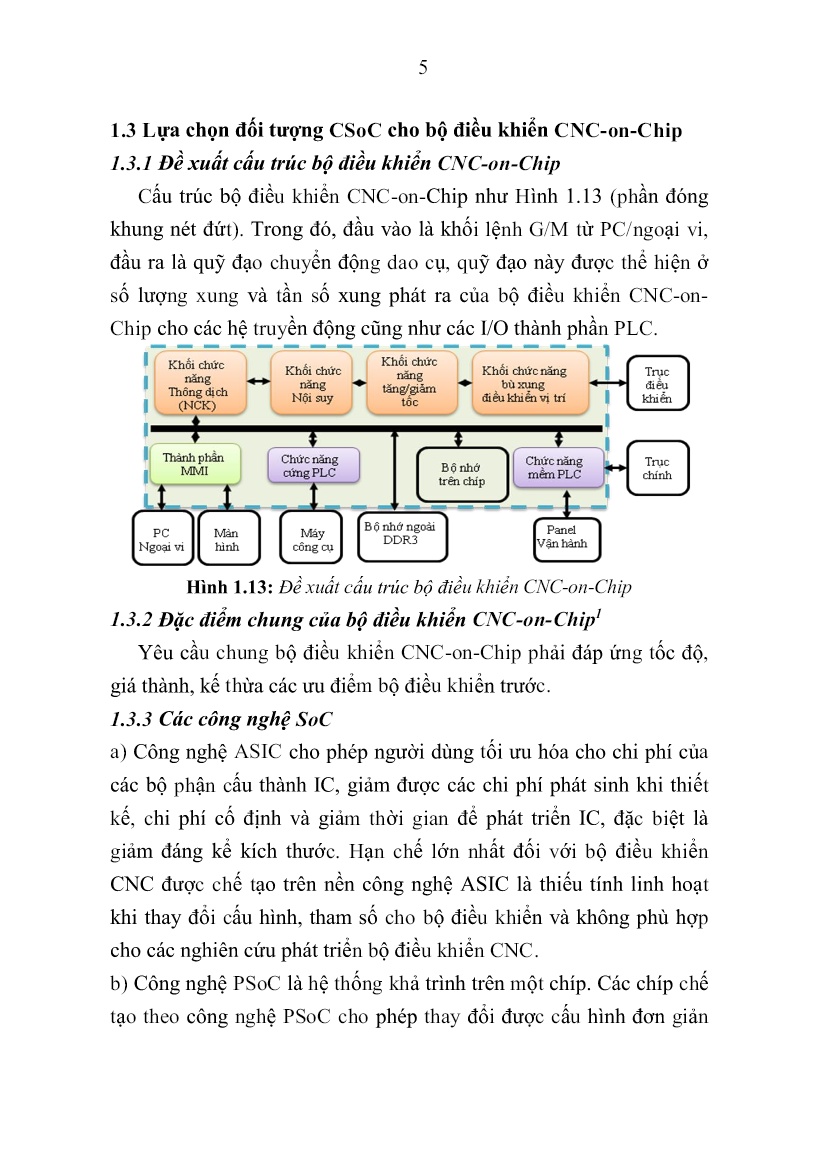

Cấu trúc bộ điều khiển CNC-on-Chip như Hình 1.13 (phần đóng

khung nét đứt). Trong đó, đầu vào là khối lệnh G/M từ PC/ngoại vi,

đầu ra là quỹ đạo chuyển động dao cụ, quỹ đạo này được thể hiện ở

số lượng xung và tần số xung phát ra của bộ điều khiển CNC-on-

Chip cho các hệ truyền động cũng như các I/O thành phần PLC.

Hình 1.13: Đề xuất cấu trúc bộ điều khiển CNC-on-Chip

1.3.2 Đặc điểm chung của bộ điều khiển CNC-on-Chip1

Yêu cầu chung bộ điều khiển CNC-on-Chip phải đáp ứng tốc độ,

giá thành, ếk thừa các ưu điểm bộ điều khiển trước.

1.3.3 Các công nghệ SoC

a) Công nghệ ASIC cho phép người dùng tối ưu hóa cho chi phí của

các ộb phận cấu thành IC, giảm được các chi phí phát sinh khi thiết

kế, chi phí cố định và giảm thời gian để phát triển IC, đặc biệt là

giảm đáng ể k kích thước. Hạn chế lớn nhất đối với bộ điều khiển

CNC được chế tạo trên nền công nghệ ASIC là thiếu tính linh hoạt

khi thay đổi cấu hình, tham số cho bộ điều khiển và không phù hợp

cho các nghiên cứu phát triển bộ điều khiển CNC.

b) Công nghệ PSoC là hệ thống khả trình trên một chíp. Các chíp chế

tạo theo công nghệ PSoC cho phép thay đổi được cấu hình đơn giản

6

bằng cách gán chức năng cho các khối tài nguyên có sẵn trên chíp.

PSoC cho phép người dùng thay đổi cấu trúc phần cứng, nhưng hạn

chế về tài nguyên.

c) Công nghệ FPGA đã xuất hiện như một giải pháp cơ bản cho vấn

đề tranh thủ thời gian và chi phí ban đầu thấp. Công nghệ FPGA cho

phép chế tạo nhanh bộ điều khiển CNC có giá thành sản phẩm thấp,

tạo nên sức cạnh tranh lớn trên thị trường. Bộ điều khiển CNC được

thực hiện bởi FPGA không khả thi nếu không có sự hỗ trợ các lõi xử

lý bên ngoài. Như vậy, FPGA tháo ỡg khó khăn cho công nghệ ASIC

về khả năng tái cấu trúc phần cứng và tùy biến tài nguyên cho công

nghệ PSoC. Song, yêu cầu một FPGA chứa ba thành phần MMI,

NCK, PLC tích hợp ba lõi xử lý riêng là vượt quá so ớv i lõi mềm có

sẵn trên FPGA.

d) Công nghệ CSoC là tích hợp thêm dòng vi xử lý ARM vào trong

một chíp cùng với FPGA để tạo nên loại chíp CSoC. CSoC được cấu

tạo bởi 2 thành phần HPS và FPGA, sự tích hợp chặt chẽ giữa hai

thành phần này cho tốc độ băng thông lên đến hơn 1.25 Gbp/s dựa

trên kiến trúc AXI.

1.3.4 Lựa chọn công nghệ SoC cho bộ điều khiển CNC-on-Chip

Qua phân tích các loại SoC, tác giả đi đến kết luận đề xuất CSoC

làm đối tượng để thiết kế bộ điều khiển CNC-on-Chip. CSoC cho

phép người dùng tùy biến cấu hình phần cứng và phần mềm cũng

như những sức mạnh khác mà CSoC ếk t thừa từ ASIC, PSoC, FPGA.

1.4 Kết luận chương 1

Đóng góp chính trong chương này là lựa chọn CSoC cho bộ điều

khiển CNC-on-Chip phù hợp các nghiên cứu, sự phát triển chung

công nghệ và đáp ứng yêu cầu thay đổi phần cứng, phần mềm của bộ

điều khiển CNC.

7

CHƯƠNG 2. THIẾT KẾ PHẦN CỨNG BỘ ĐIỀU KHIỂN CNC-

ON-CHIP

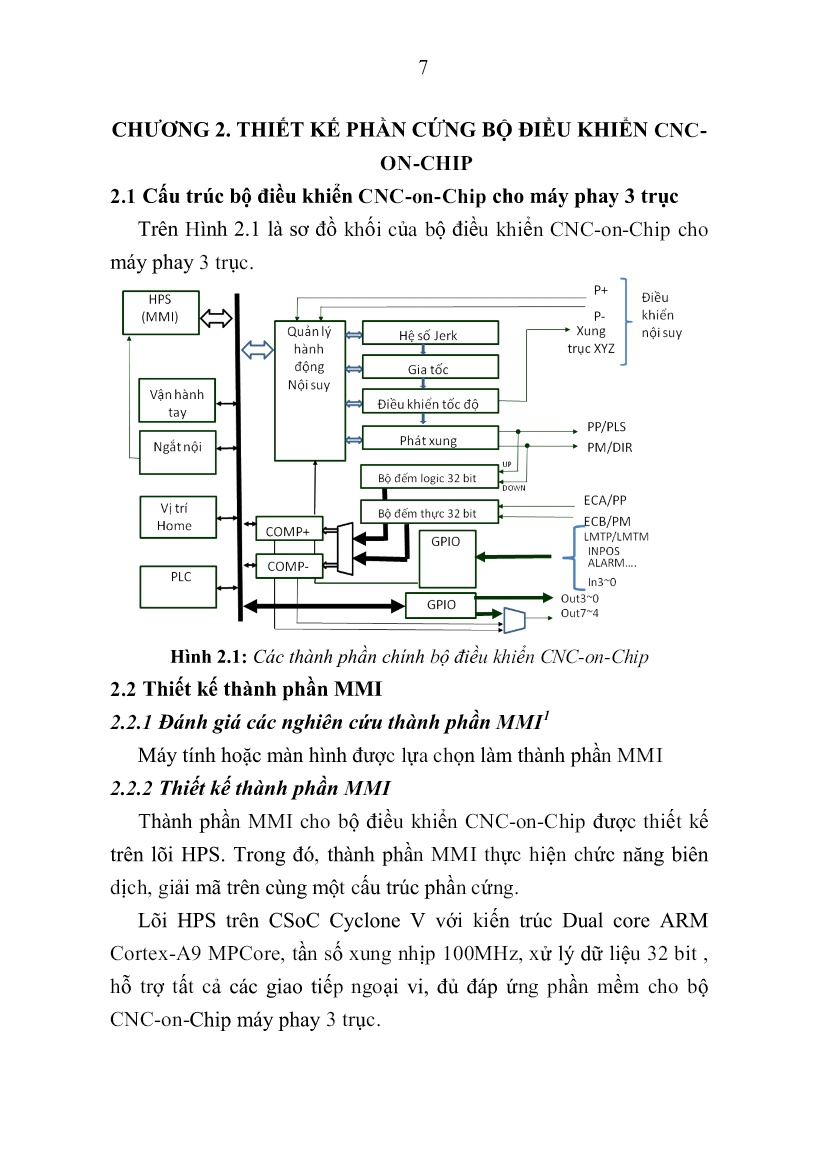

2.1 Cấu trúc bộ điều khiển CNC-on-Chip cho máy phay 3 trục

Trên Hình 2.1 là sơ đồ khối của bộ điều khiển CNC-on-Chip cho

máy phay 3 trục.

Hình 2.1: Các thành phần chính bộ điều khiển CNC-on-Chip

2.2 Thiết kế thành phần MMI

2.2.1 Đánh giá các nghiên cứu thành phần MMI1

Máy tính hoặc màn hình được lựa chọn làm thành phần MMI

2.2.2 Thiết kế thành phần MMI

Thành phần MMI cho bộ điều khiển CNC-on-Chip được thiết kế

trên lõi HPS. Trong đó, thành phần MMI thực hiện chức năng biên

dịch, giải mã trên cùng một cấu trúc phần cứng.

Lõi HPS trên CSoC Cyclone V với kiến trúc Dual core ARM

Cortex-A9 MPCore, tần số xung nhịp 100MHz, xử lý dữ liệu 32 bit ,

hỗ trợ tất cả các giao tiếp ngoại vi, đủ đáp ứng phần mềm cho bộ

CNC-on-Chip máy phay 3 trục.

8

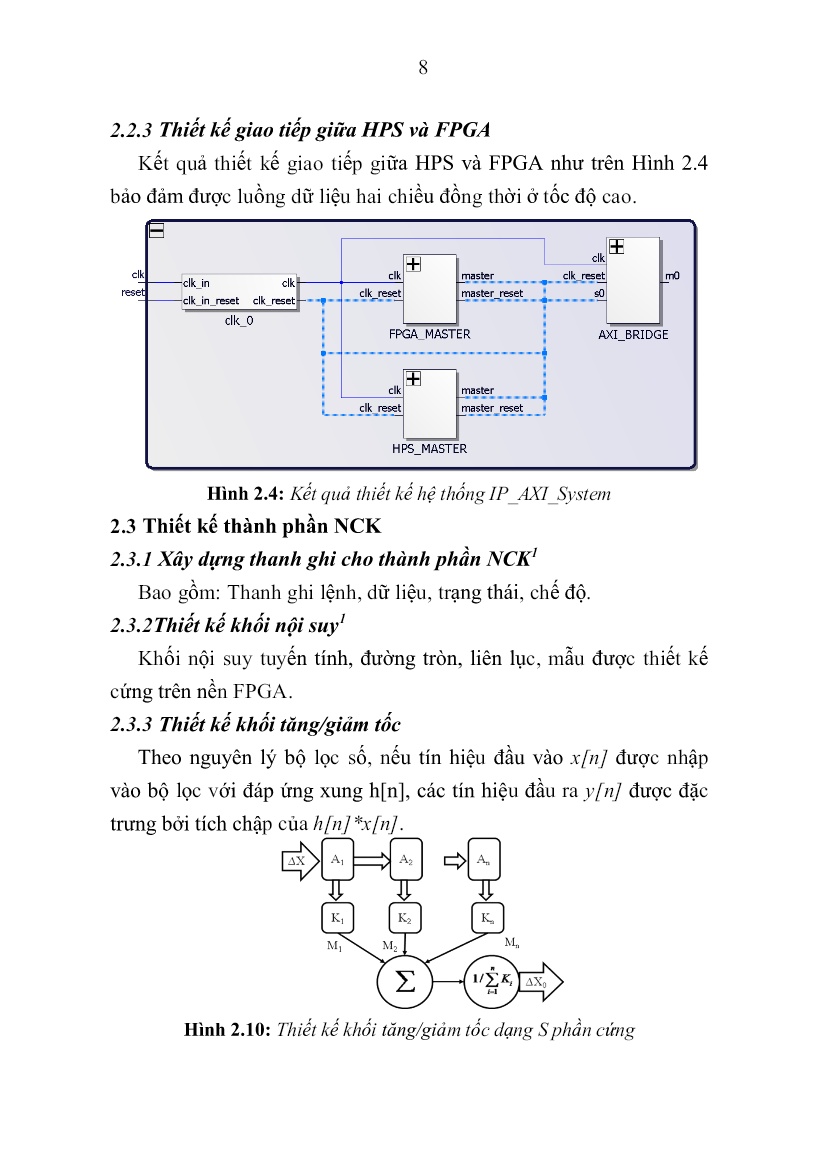

2.2.3 Thiết kế giao tiếp giữa HPS và FPGA

Kết quả thiết kế giao tiếp giữa HPS và FPGA như trên Hình 2.4

bảo đảm được luồng dữ liệu hai chiều đồng thời ở tốc độ cao.

Hình 2.4: Kết quả thiết kế hệ thống IP_AXI_System

2.3 Thiết kế thành phần NCK

2.3.1 Xây dựng thanh ghi cho thành phần NCK1

Bao gồm: Thanh ghi lệnh, dữ liệu, trạng thái, chế độ.

2.3.2Thiết kế khối nội suy1

Khối nội suy tuyến tính, đường tròn, liên lục, mẫu được thiết kế

cứng trên nền FPGA.

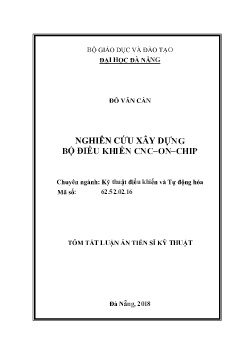

2.3.3 Thiết kế khối tăng/giảm tốc

Theo nguyên lý bộ lọc số, nếu tín hiệu đầu vào x[n] được nhập

vào bộ lọc với đáp ứng xung h[n], các tín hiệu đầu ra y[n] được đặc

trưng bởi tích chập của h[n]*x[n].

Hình 2.10: Thiết kế khối tăng/giảm tốc dạng S phần cứng

9

Đối với một số nội suy trên phần mềm thì tăng/giảm tốc cũng

được thực hiện trên phần mềm. Ngược lại, nội suy phần cứng sẽ được

tăng/giảm tốc bằng cấu trúc phần cứng (Hình 2.10).

2.3.4 Thiết kế khối bù feedforward cho điều khiển vị trí1

Sử dụng bộ đếm tốc độ cao trên FPGA để bắt xung Encoder.

2.4 Thiết kế thành phần PLC

2.4.1 Các nghiên cứu thành phần PLC1

Cấu trúc thành phần PLC là lõi mềm Nios và phần cứng FPGA.

2.4.2 Thiết kế thành phần PLC

Kết quả thiết kế thành phần PLC được thực hiện trên CSoC (Hình

2.14) mang lại nhiều ưu điểm hơn. Cụ thể ở các tiêu chí: truyền thông

“on chip” với thành phần NCK, MMI, giảm tải CPU nhờ một số thiết

kế cứng trên FPGA, tùy biến các cấu hình I/O...

Hình 2.14: Kết quả thiết kế thành phần PLC

2.5 Tổng hợp thiết kế phần cứng bộ điều khiển CNC-on-Chip

Kết quả biên dịch phần cứng bộ điều khiển CNC-on-Chip trên nền

công nghệ CSoC Cyclone V như trên Hình 2.16. Trong đó, ALMs

10

chiếm 17%, thanh ghi 7117, số chân 59%, khối nhớ 26%, PLL 17%,

DLL 25%... Như vậy, thiết kế kiến trúc bộ điều khiển CNC-on-Chip

cho máy phay 3 trục với đầy đủ các thành phần và chức năng, cho

thấy các tham số chiếm phần nhỏ so với tài nguyên có sẵn trên chíp.

Vì vậy, việc chọn lựa đối tượng CSoC để xây dựng bộ điều khiển

CNC-on-Chip là hoàn toàn phù hợp, đáp ứng được tài nguyên, ngay

cả các bộ điều khiển CNC máy công cụ nhiều hơn 3 trục.

Hình 2.16: Tổng hợp phần cứng trên chíp Cylone V SoC

2.6 Kết luận chương 2

Đóng góp trong chương 2 là nội dung đã đáp ứng được mục tiêu

đặt ra ở đầu chương là thiết kế thành công phần cứng của bộ điều

khiển CNC-on-Chip cho máy phay 3 trục dựa trên công nghệ CsoC.

Vì vậy, tài nguyên dòng công nghệ CsoC là đủ đáp ứng thiết kế bộ

điều khiển CNC-on-Chip.

11

CHƯƠNG 3. XÂY DỰNG CHỨC NĂNG TẬP LỆNH BỘ ĐIỀU

KHIỂN CNC-ON-CHIP

3.1 Xây dựng chức năng tập lệnh thành phần MMI

Xây dựng chức năng thành phần MMI bởi ngôn ngữ C/C++ dựa

trên lõi HPS sau khi cấu hình phần cứng ở chương 2. Chức năng này

phản ánh quá trình biên dịch tập lệnh M/G của người dùng trên phần

mềm và trình bày chi tiết phụ lục 3.

3.2 Xây dựng tập lệnh thành phần NCK

3.2.1 Chức năng giải mã khối lệnh

Sau khi biên dịch, các khối lệnh được giải mã trên lõi của bộ điều

khiển CNC. Các biến được tách và gán giá trị trên các thanh ghi

tương ứng cho từng lệnh và chuyển tải cho chức năng nội suy.

3.2.2 Chức năng nội suy

a) Nội suy tuyến tính:

Hình 3.4: Đề xuất thuật toán đồng bộ xung phần cứng

Thực hiện mô phỏng thuật toán đề xuất như Hình 3.4 bằng phần

mềm Modelsim với các tham số như sau: Điểm bắt đầu (1,1,1); điểm

kết thúc (10,6,8). Hình 3.5 là kết quả mô phỏng sau khi sử dụng thuật

toán đồng bộ xung phần cứng.

12

Hình 3.6: Mô phỏng thuật toán đồng bộ xung phần cứng nội suy tuyến tính

Trên Hình 3.6 mô tả xung trên 3 trục với chiều dài lần lượt

(X,Y,Z) = (9,5,7). Hệ số mô phỏng k =1 BLU số xung trên các trục

tương ứng lần lượt (9,5,7), sự phát xung của các trục là đồng thời.

b) Nội suy đường tròn

Đề xuất tác giả là cải tiến thuật toán xấp xỉ bậc thang dựa trên

phần cứng CSoC (Hình 3.8), cụ thể:

+ Tăng 1 BLU cho hướng X,

+ Giảm 1 BLU cho hướng Y,

+ Tăng 1 BLU cho hướng X, đồng thời giảm 1 BLU hướng Y.

Hình 3.8: Thuật toán xấp xỉ bậc thang trước và sau cải tiến

13

Hình 3.9: Kết quả mô phỏng thuật toán xấp xỉ bậc thang trước (a) và sau

cải tiến (b)

Biểu diễn thuật toán xấp xỉ bậc thang bằng cách thực hiện nội suy

các tham số như sau: Điểm bắt đầu (0,10), điểm kết thúc (10,0),

hướng nội suy CW, BLU=1. Trục X có 11 xung tương ứng tại các ịv

trí 1, 3, 4, 5, 6, 8, 9, 11, 13, 16 và 21 BLU. Tương tự, trục Y có 10

xung tại các vị trí 2, 7, 10, 12, 14, 15, 17, 18, 19 và 20 BLU.

Trên Hình 3.9a là quỹ đạo chuyển động của các trục X, Y khi sử

dụng thuật toán xấp xỉ bậc thang chưa xét đến đề xuất của tác giả.

Kết quả Hình 3.9b là sử dụng thuật toán xấp xỉ bậc thang cải tiến dựa

trên CSoC. Các sai lệch tối đa của thuật toán này là 1/2 BLU và tính

chính xác của thuật toán này là tốt hơn so với thuật toán xấp xỉ bậc

thang (sai lệch 1 BLU), số lần lặp (15 lần) nhỏ hơn 30% so với các

thuật toán ấx p xỉ bậc thang (21 lần).

Sử dụng ngôn ngữ Verilog để xây dựng thuật toán trên cấu trúc

phần cứng của FPGA, có các tham số như trên, dX, dY là dãy phát

xung và X, Y (Hình 2.11) là quỹ đạo trên các trục tương ứng, các kết

quả hoàn toàn phù hợp với nghiên cứu lý thuyết và biểu diễn Hình

3.9.

14

Hình 3.11: Kết quả xây dựng thuật toán xấp xỉ bậc thang cải tiến

3.2.3 Chức năng tăng/giảm tốc

a) Xây dựng chức năng tăng/giảm tốc ADCBI: Nội dung của thuật

toán “LookAhead” là giảm tốc độ cắt đã được giới thiệu bằng cách

xem xét ra lệnh tốc độ cắt và chiều dài của khối tiếp theo. Tốc độ

khởi động của khối hiện lại phụ thuộc tốc độ của khối kế tiếp, được

xác ịđ nh phương trình (3.10) và độ dài gia tốc (3.11).

2

V0 Vf 2 AL (3.10)

97

S Jt 4/3 (3.11)

ac/024

Thuật toán được xây dựng trên Hình 3.12 – Hình 3.14 để xác định

tốc độ kết thúc của khối phía trước phụ thuộc khối phía sau.

Hình 3.12 Thuật toán xác định tốc độ kết thúc; Hình 3.13: tốc độ bắt đầu

và Hình 3.14 tốc độ khối hiện tại

15

Kết quả thực hiện thuật toán trên cho N bước, cụ thể trong trường

hợp này sử dụng 15 điểm trên nửa đường tròn với 14 đoạn lặp thể

hiện trên Hình 3.16. Kết quả ổn định Fmax = 304,5 < F =400 mm/phút

Hình 3.16: Tốc độ sau khi thực hiện tăng/giảm tốc 15 bước

b) Xây dựng chức năng tăng/giảm tốc ADCAI:

Phần thứ hai khối ADCAI xây dựng trên nền FPGA, chương trình

mô tả gia tốc ADCAI dạng S được viết bằng ngôn ngữ Verilog.

Hình 3.20: Kết quả mô phỏng gia tốc ADCAI trên phần cứng

Các ế k t quả thực nghiệm trên phần cứng của CSoC cho khối

tăng/giảm tốc như Hình 3.20. Kết quả này cho thấy, khối gia tốc

được thực hiện dạng S trên nền CsoC, cụ thể: Các giá trị vận tốc là

{11, 15, 24, 49, 107, 205, 302, 361, 386, 395, 398 và 400}. Và quá

trình chuyển đổi tốc độ từ 400 sang 200 được thực hiện theo sự giảm

tốc dạng S là { 400, 398, 395, 361, 302, 205, 200}.

16

3.2.4 Chức năng điều khiển vị trí

Bộ lọc nhân quả sử dụng dữ liệu vị trí hiện tại và dữ liệu vị trí từ

một, hai bước trước đó. Để đánh giá ợđư c ưu điểm điều khiển vị trí

từ phương pháp bù feedforward, ta tiến hành mô phỏng kết quả quỹ

đạo bám của hệ thống. Với kết quả mô phỏng khi sử dụng điều khiển

bù feedforward (Hình 3.27) cho thấy khả năng đáp ứng tốt khi điều

khiển vị trí đặt.

Hình 3.27: Kết quả thực hiện bù xung điều khiển vị trí

3.3 Xây dựng tập lệnh thành phần PLC

3.3.1 Xây dựng chức năng mềm thành phần PLC

Tương tự như mã G, mã M cũng có vai trò điều khiển hệ thống

ngoại vi của bộ điều khiển CNC. Một chương trình được xây dựng để

kiểm tra mã M và thay dao cụ trên phần mềm bởi ngôn ngữ C/C++

trên phần mềm của thành phần PLC. Thành phần PLC của bộ điều

khiển CNC-on-Chip thực hiện các chức năng xử lý T, S, M-code,

điều khiển logic trục chính và giao tiếp với NCK.

3.3.2 Xây dựng chức năng cứng thành phần PLC

Kết quả mô phỏng quá trình thiết kế chức năng lọc trên phần cứng

CSoC như Hình 3.32, thời gian đáp ứng đầu ra theo đầu vào là 5 chu

kỳ clock, và 2 chu kỳ clock. Đối với 2 chu kỳ clock thời gian đáp ứng

nhanh hơn nhưng lại không khử nhiễu tại thời điểm 610ps. Vì thế,

các thiết kế được lựa chọn mức lọc sao cho phù hợp với các ứng

17

dụng cụ thể. Ngoài ra, người dùng có thể xây dựng thuật toán xác

định mức lọc từ chương trình phần mềm trên CPU.

Hình 3.32: Mô phỏng xây dựng phần cứng I/O với lọc 2 mức

3.4 Kết luận chương 3

- Đề xuất thuật toán đồng bộ xung phần cứng cho nội suy tuyến

tính, mang lại tốc độ nội suy nhanh hơn 140% so với các phép ộn i

suy tuyến tính của bộ điều khiển CNC trước đây.

- Đề xuất cải tiến thuật toán xấp xỉ bậc thang cho nội suy đường

tròn, rút ngắn được thời gian nội suy 30% so với thuật toán trước khi

cải tiến và độ chính xác cho quỹ đạo đặt là giảm sai lệch từ 1 BLU

xuống còn 0,5 BLU.

- Xây dựng bộ tăng/giảm tốc linh hoạt kiểu S trên phần cứng và

phần mềm trước và sau nội suy trên nền CSoC giải quyết được các

vấn đề: giảm sai lệch trong tăng/giảm tốc, rung giật hữu hạn do tăng

tốc/giảm tốc trong cácchuy ển động đặc biệt gây ra.

- Xây dựng thành phần PLC cùng với thành phần NCK, MMI trên

cùng 1 chíp duy nhất, thực hiện một số chức năng phần cứng để giảm

tải cho CPU.

18

CHƯƠNG 4. KẾT QUẢ MÔ PHỎNG VÀ THỰC NGHIỆM

4.1 Bài toán thực nghiệm

Bài toán thực nghiệm bảo đảm rằng các ấv n đề đóng góp của luận

án được thể hiện trong chương này, cũng là kiểm chứng một cách cụ

thể cho các đề xuất của tác giả.

Hình 4.1: Quỹ đạo dao cụ cho bài toán thực nghiệm

4.2 Kết quả mô phỏng

4.2.1 Mô phỏng chức năng tăng/giảm tốc qua lệnh G00

Phản ánh đóng góp tăng/giảm tốc dạng S trên phần cứng. Đối với

chuyển động tốc độ mặc định G00, cài đặt tần số 5kHz, hành trình di

chuyển trục Z là 20 mm, lựa chọn tỷ lệ cài đặt bộ CNC-on-Chip

k=500xung/mm, thì mất 10.000 xung và thời gian hành trình trục Z là

10.000 xung/5kHz = 2s. Kết quả mô phỏng gia tốc thể hiện như Hình

4.2. là 2,2s; quá trình gia tốc bắt đầu và kết thúc chu trình gia công.

Hình 4.2: Kết quả mô phỏng khối lệnh N30 G00 Z20

19

4.2.2 Mô phỏng chức năng nội suy tuyến tính qua lệnh G01

Đối với tốc độ ăn dao cực đại Fmax = 1000 mm/phút được xác lập

tần số 5kHz. Như vậy, với tốc độ ăn dao F = 400mm/phút (khối lệnh

N60 G01 X100 Y60 Z80 F400) thì tần số lý thuyết là 2kHz (trục dài).

Hình 4.3: Kết quả mô phỏng khối lệnh N60 G01

Kết quả mô phỏng trên Hình 4.3, phản ánh đúng các nghiên cứu

đóng góp của luận án về tần số và thời gian nội suy.

4.2.3 Mô phỏng chức năng nội suy đường tròn qua lệnh G02

Sự phát xung đồng thời của 2 trục được thể hiện ở thời gian kết

thúc chu trình là 35s. Hình 4.4 phản ánh các nội dung đã nghiên cứu

rút ngắn thời gian nội suy, giảm sai lệch từ 1BLU xuống 0,5BLU.

Hình 4.4: Kết quả mô phỏng khối lệnh N80 G02 (C D)

4.3 Kết quả thực nghiệm

4.3.1 Giải pháp cho hệ thống thực nghiệm

Hệ thống thực nghiệm được lắp ráp như Hình 4.5. Tác giả tiến

hành cài đặt phần cứng, phần mềm và chương trình người dùng.

20

Hình 4.5: Sơ đồ đấu nối thực nghiệm bộ điều khiển CNC-on-Chip

4.3.2 Thực nghiệm hoạt động phần cứng và phần mềm

Hình 4.6 minh chứng chương trình phần mềm mà tác giả đã

nghiên cứu, xây dựng trên bộ CNC-on-Chip. Kết quả này, cho thấy

khả năng làm việc tương thích giữa phần cứng và phần mềm được

xây dựng trên cùng một chíp.

Hình 4.6: Thực nghiệm phần mềm bộ điều khiển CNC-on-Chip

4.3.3 Thực nghiệm tăng/giảm tốc qua chuyển động thẳng lệnh G00

Thực nghiệm thể hiện quá trình tăng tốc và giảm tốc cho thấy

xung được phân bổ theo quy luật hàm S thể hiện qua tần số xung bắt

21

đầu và kết thúc, tần số ổ định 5kHz, thời gian nội suy

4,4x500ms=2,2s như Hình 4.7 phù hợp với lý thuyết và mô phỏng.

Hình 4.7: Kết quả thực nghiệm lệnh G00

Để dễ dàng nhìn thấy đề xuất, tác giả biểu diễn dưới dạng đường

vận tốc của quá trình tăng/giảm tốc.

Hình 4.8: Biểu diễn vận tốc khi thực hiện tăng giảm tốc ở 1Hz

22

4.3.4 Thực nghiệm chức năng nội suy đường thẳng qua G01

Kiểm chứng đóng góp thuật toán đồng bộ xung phần cứng thể

hiện Hình 4.11, toàn bộ dãy xung thời gian phát xung cho 3 trục

tương ứng 25s, phù hợp với các ếk t quả nghiên cứu lý thuyết.

Hình 4.11: Toàn bộ hành trình trên các trục X, Y, Z cho G01

Để có cái nhìn trực quan hơn, tác giả biểu diễn quỹ đạo chuyển

động truyến tính của các trục ứng với thuật toán đã đề xuất.

Hình 4.14: Đánh giá quỹ đạo G01 giữa thuật toán từ tham chiếu (tuần tự)

và thuật toán đồng bộ xung phần cứng (song song)

23

4.3.5 Thực nghiệm chức năng nội suy đường tròn G02

Một đóng góp khác của tác giả trong luận án này là ảc i tiến thuật

toán xấp xỉ bậc thang cho phép nội suy đường tròn dựa trên phần

cứng. Kết quả này cho thấy thời gian thực hiện sau cải tiến ngắn hơn

5x5s=25s so với chưa cải tiến là 5x10s=50s và độ chính xác cao hơn

0,5 BLU so với chưa cải tiến là 1 BLU đối với hai trục.

Để thể hiện rõ hơn, tác giả tiến hành biểu diễn thực nghiệm với hệ

số xung k=1 xung/mm kết quả đo được Hình 4.17.

Hình 4.17: Biểu diễn thuật toán xấp xỉ bậc thang trước và sau cải tiến

4.3.6 Thực nghiệm chức năng thành phần PLC

Một trong các đóng góp của tác giả này là tích hợp toàn bộ thành

phần PLC lên trên cùng một chíp chung với thành phần MMIFile đính kèm:

luan_an_nghien_cuu_xay_dung_bo_dieu_khien_cnconchip.pdf

luan_an_nghien_cuu_xay_dung_bo_dieu_khien_cnconchip.pdf